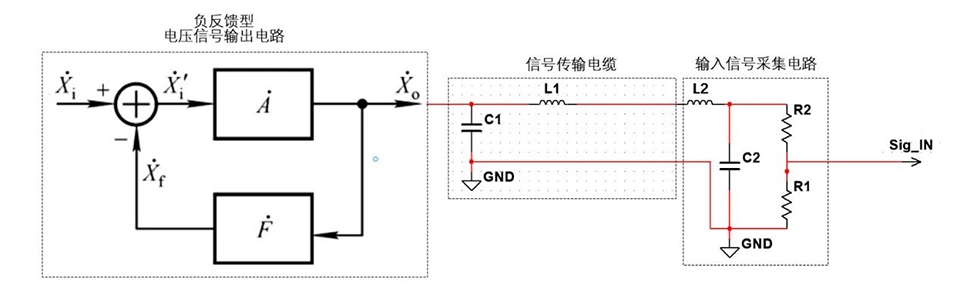

그림 1 에서와 같이,전송 전압의 원본 신호는 주로 3 부분으로 구성:

- 부정적인 의견 유형 전압 신호 출력 회로.

- 신호 전송 케이블이 있습니다. 그 중 C1 및 L1 는 기생 커패시턴스 및 기생 인덕턴스의 케이블 및 그들의 매개 변수를 직접 관련된 케이블의 길이와 배선 유형입니다.

- 입력 신호를 취득 회로입니다. 그 중,L2and C2 낮은 패스 필터 회로에 배치 될 수 있는 부분에서의 샘플링 회로입니다.

에 대한 부정적인 의견을 전압 신호 출력 회로,계산식의 입력 신호는 다음과 같습니다:

∣Xi'∣=∣시∣−∣Xf∣

면 단계 ofXXf∣이 만료되거나 지연으로 180°,계산식의 입력 신호가 다음과 같은 형태:

∣Xi'∣=∣시∣+∣Xf∣

다시 말해서,의 부재에서 입력 신호(XiXiXi0)피드백 신호(XXf∣)을 유지하는 출력 신호(|X0|)및 출력 신호(|X0|)을 유지 관리합 피드백 신호(XXf∣). 이 시점에서,자가 흥분하는 진동을 형성합니다.

모두 모두,다음과 같은 두 가지 조건을 전제 조건을 자기에 대한 흥분하는 진동:

- |AF|>1

- φA+φF=(2n+1)Π

치지 않는 단계에 차이는 루프에서 오는가?

기생 C1 및 L1 에서 신호 전송 케이블,L2,C2 입력 신호를 취득 회로,그리고 필터 콘덴서에는 신호 출력 회로 모든 원인 단계에서 차이나 히스테리시스. 최종 단계에 차이는 합의 이상 차이점이 있습니다. 는 경우에는 기간이 연체 또는 히스테리시스가 180°,그것을 가능하게 자극하는 진동.

을 방지하는 방법 자가 흥분하는 진동?

우리만 있는지 확인해야의 범위 내에서 적용되는 주파수 도메인 전술한 두 가지 조건을 충족 할 수 없습니다 같은 시간에,그래서 자기 흥분하는 진동을 피할 수 있습니다.

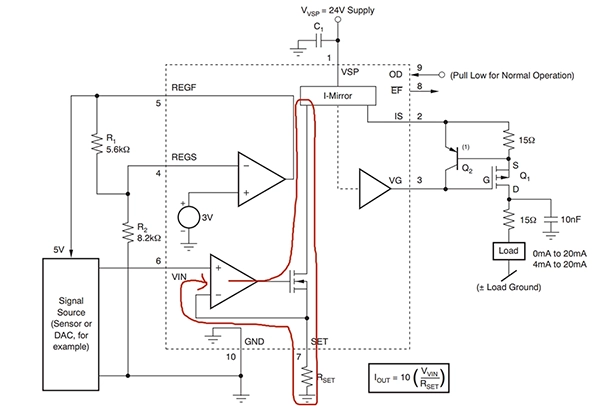

그림 2 와 같이:

f 애플리케이션은 다음과 같은 주파수 루프의 이득을 20log|AF|방울을 0dB.

f o 은 주파수에서 위상 차이가 루프의 미만 -180°.

따라서,단계에 차이 만료되거나 히스테리시스가 180°,이득의 반복이 아래로 떨어 0,과 회로 안정되어 있습니다.

상대적으로 말해서,왜 현재의 소신호하기 쉽지 않 진동?

그림 2 와 같이 출력 전류의 소스로 현재 널리 사용되는 거울이 현재 소스입니다. 는 부정적인 의견을 규정 루프가 포함되어만 한쪽의 거울 현재의 원천으로 식별됩니다. 따라서,외부 부하가 회로에 거의 영향을 미치지의 위상 차이점을 얻을의 피드백 루프입니다. 한 매개 변수의 내부의 피드백 루프 제어,아동가 발생합니다.

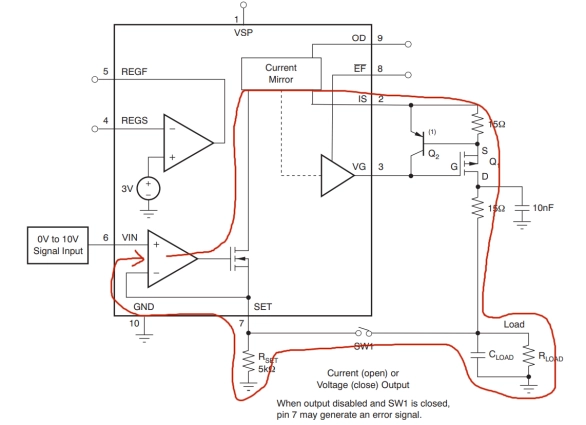

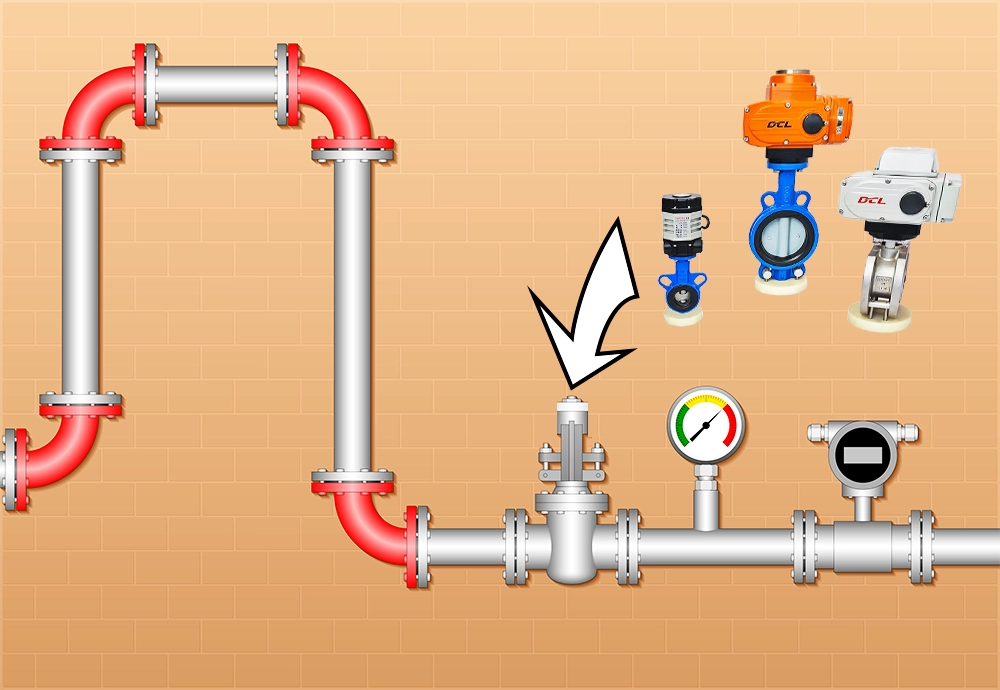

그림 3 과 같이,피드백의 포인트 전압 신호를 소스에 위치하고 있 출력 포인트의 회로입니다. 따라서,피드백 루프를 포함한 내부 회로에 의해 표시 빨간 라인과 외부 케이블 및 샘플링 회로입니다. 이 때문에 전기적 매개변수의 외장 케이블 또는 샘플링는 케이블 변화,위상 차이의 이익에 부정적인 피드백 루프도 변경됩니다. 이러한 변경을 만족은 두 가지 조건이 자기의 흥분하는 진동,진동 발생합니다.

Hubei 공용 네트워크 보안 No.42018502006527

Hubei 공용 네트워크 보안 No.42018502006527