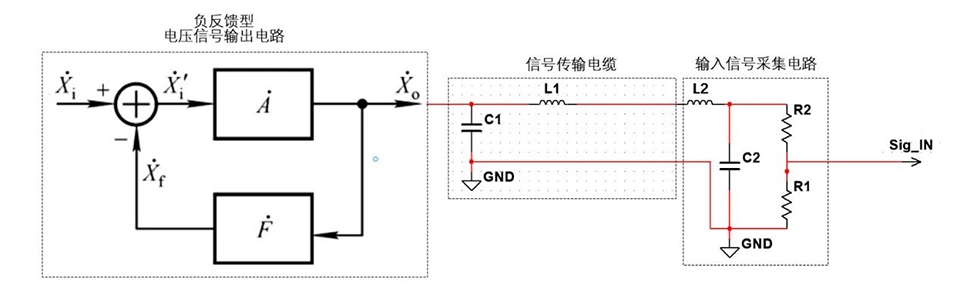

図1の透過率の電圧信号を主成3部:

- 負のフィードバック型の電圧信号を出力回路です。

- 信号伝送ケーブルにします。 このうち、C1L1における寄生容量および寄生インダクタンスのケーブル、およびそのパラメータに直接関連する長さのケーブル-配線タイプです。

- 入力信号を取得。 このうち、L2およびC2は低通過フィルタ回路内の一部のサンプリング回路。

のための負のフィードバック電圧信号を出力回路の計算式は、入力信号としており:

∣Xi'∣=∣Xi∣−∣Xf∣

の相ofXXf∣の満了日または遅れを180°の計算式は、入力信号が以下のフォーム:

∣Xi'∣=∣Xi∣+∣Xf∣

つまり、入力信号(XiXiXiが0の)は、フィードバック信号(XXf∣を維持しており、出力信号|X0|)と、出力信号|X0|)回のフィードバック信号(XXf∣). この時の自励振動が形成されている。

すべての条件を前提条件の自励振動:

- |AF|>1

- φA+φF=(2n+1)Π

の位相差のループから来るのでしょうか?

寄生C1L1、信号伝送ケーブル、L2およびC2の入力信号を取得回路、フィルタコンデンサの信号出力回路にある全ての原因の相違いか事前にヒステリシス. 最後の位相差額のこれらの相違いがある。 場合、期間の延滞またはヒステリシスは180°で自励発振.

などを避けるための自励発振?

することを確実にしなければならな範囲での周波数領域"においては、前述の二つの条件をできることを示すためには同時に、この自励振動を避けることができます。

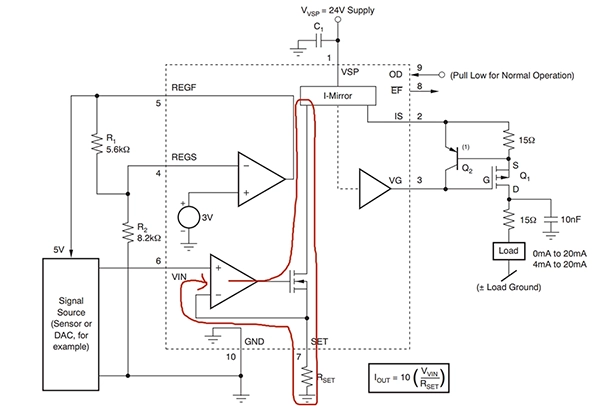

図2:

f cの周波数のループゲインの20log|AF|滴を0dB.

アナログ、デジタル入出力は周波数の位相差のループは以下の-180°となっています。

したがって、位相差の満了日又はヒステリシスは180°のゲインのループ以下0、および回路が安定しています。

比較的といえば、なぜ現在のソース信号は容易ではない振動は?

図2に示されるように構成され、出力の電流電源は、現在広く使用されるミラー電流のソースです。 その負のフィードバック制御ループのみを含む片側のミラー電流源を特定することによります。 そのため、外部負荷回路の位相差を得るのにフィードバックする どのパラメータ内のフィードバックループ制御、振動が発生します。

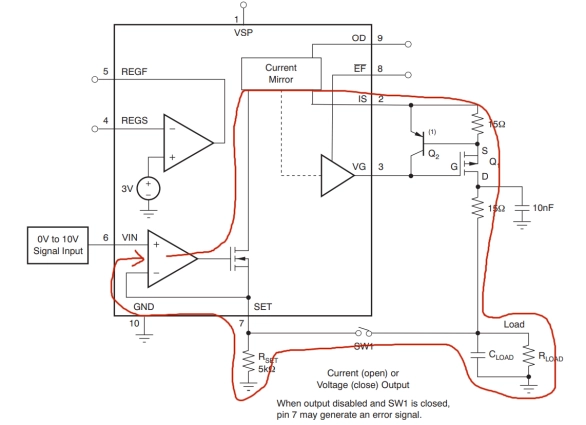

図3に示すように、フィードバックポイントの電圧信号を出力点の回路です。 そのため、フィードバックループの内部回路を赤線、外部ケーブルおよびサンプリング回路。 このように、電気的パラメータは外部のケーブルまたはサンプリングケーブル変更により、位相差益負のフィードバックループも変化します。 この変更を満たす条件を自励振動の振動が発生します。

湖北の公共のネットワークの安全No.42018502006527

湖北の公共のネットワークの安全No.42018502006527